# Scheme and Syllabus of M. Tech. ECE (VLSI) (2024-2025 onwards)

# Offered by:

# **Department of Electronics & Communication Engineering**

# NATIONAL INSTITUTE OF TECHNOLOGY DELHI Delhi-110036

(An autonomous Institute under the aegis of Ministry of Education, Govt. of India)

<sup>\*</sup>Approved in the 3<sup>rd</sup> Meeting of Board of Studies of the Dept. of ECE, held on February 23, 2024 and in line with the recommendation of the Honourable Senate in the 17<sup>th</sup> Senate Meeting held on May 30, 2024.

# Department of Electronics and Communications Engineering National Institute of Technology Delhi

#### 1.1 About the Department

Welcome to the Department of Electronic and Communication Engineering (ECE), National Institute of Technology Delhi. It was established in 2010, immediately with the beginning of the Institute under the aegis of the Ministry of Human Resource and Development (MHRD), Govt. of India. Currently, Department is offering one Undergraduate Program as B. Tech (ECE) and two Postgraduate programs as M. Tech. ECE and M. Tech. ECE (VLSI). The Department also offers Ph.D. and Post-Doctoral Fellowship (PDF) Programme in relevant areas. It has excellent laboratories and research facilities in electronic devices and circuits, electronic measurement and instrumentation, microprocessor and microcontroller, microwave and antenna design, optical fiber communication and optical device, multimedia, and advanced communication and VLSI design automation and simulation laboratory. The Department has received projects, grants, and fellowships from the Ministry of Electronics and Information Technology (MeitY), the Department of Science and Technology (DST)-SERB, and other funding agencies. The Department has active collaborations with academic & research institutes in India and abroad.

The Department of ECE has a blend of young as well as experienced dynamic faculty members and is committed to providing quality education and research in the field. Faculty members of the department have excellent academic & research credentials and published numerous peer-reviewed journal articles/ papers, Books, Book Chapters, etc. in the diversified field and have adequate experience in advanced research. The department of ECE provides a creative learning environment to the students for excellence in technical education. Here the students learn to face the challenges related to emerging technologies in electronics and communication engineering. The department of ECE promotes a self-learning attitude, entrepreneurial skills, and professional ethics. The department hopes to achieve the national goals and objectives of industrialization and self-reliance. As a result, it hopes to produce post graduates with strong academic and practical backgrounds so that they can fit into the academia, research and industry.

#### 1.2 Vision

Create an educational environment to prepare the students to meet the challenges of the modern electronics and communication industry through state of art technical knowledge and innovative approaches beneficial to society.

#### 1.3 Mission

- To promote teaching and learning by engaging in innovative research and by offering state-of- the-art undergraduate, postgraduate, and doctoral programs.

- To cultivate an entrepreneurial environment and industry interaction leading to the emergence of creators, innovators, and leaders.

- To promote co-curricular and extra-curricular activities for the overall personality development of the students.

- Building of responsible citizens through awareness and acceptance of ethical values

#### M. Tech. in Electronics and Communication Engineering (VLSI Design)

#### 2.1 Preamble

**M. Tech. ECE (VLSI) program** offered at NIT Delhi is designed to equip the students with a unique blend of skill sets that include:

- Strong theoretical and experimental foundation

- Predominantly experiment oriented approach with access to well-equipped and specialized laboratories, and supervised internship/ Thesis work.

- Hands-on technical training

- Life skills orientation

- Hard and soft skills

- Business perspective, along with emphasis on innovation and entrepreneurship

#### 2.2 Salient Features:

- Minimum Credits requirements for completion of M. Tech ECE (VLSI) program is 80.

- The Curriculum is based on the guidelines of National Education Policy (NEP) 2020.

- The curriculum has embedded the Multi Exit/ Multi Entry in the M. Tech program.

- The curriculum is designed to meet the prevailing and ongoing industrial requirements.

- The curriculum includes Project based Education with adequate exposure for Thesis work.

- The curriculum is flexible and offers adequate Choice of Electives (Program Elective Courses).

- The curriculum inherits the Value based Education aims the Holistic Development of the students.

- The Curriculum offers Digital Pedagogy & Flipped Learning with adequate motivation for Entrepreneurship/ Start-ups.

#### 2.3 Cardinal Mention

Students exiting after completing  $1^{\text{st}}$  Year will be awarded Post Graduate Diploma in ECE (VLSI) respectively. A minimum Credit requirement for Post Graduate Diploma is 40 Credits

#### 2.4 Program Educational Objectives (PEOs)

| PEO-1 | To be technically competent in the design, development, and implementation of    |

|-------|----------------------------------------------------------------------------------|

|       | VLSI circuits and systems to solve complex problems in the domain of electronics |

|       | and communication.                                                               |

| PEO-2 | Students shall be competent in adapting to new technologies for designing        |

|       | and implementation as well as lead research in order to achieve excellence       |

|       | in their professional career.                                                    |

| PEO-3 | Enfold the capability to expand horizons beyond engineering for creativity,      |

|       | innovation and entrepreneurship.                                                 |

| PEO-4 | Acquire competence and ethics for social and environmental sustainability with a |

|       | focus on the welfare of humankind.                                               |

## 2.5 Program Outcomes (POs)

| PO-1 | Apply the knowledge of science, mathematics, and engineering principles for a problem-solving attitude and to acquire sound knowledge in the area of the VLSI domain.                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PO-2 | To design and analyze complex electronic circuits, using appropriate analytical methods as well as front-end and backend tools including prediction and modelling with an understanding of the limitations. |

| PO-3 | An ability to independently carry out research /investigation and development work to solve practical problems and have the preparedness for lifelong learning.                                             |

| P0-4 | Ability to design and conduct experiments, as well as to analyse and interpret data, and synthesis of information.                                                                                          |

| PO-5 | To comprehend and write effective reports and design documentation by adhering to appropriate standards and making effective presentations.                                                                 |

| P0-6 | Students will have a clear understanding of professional and ethical responsibility.                                                                                                                        |

#### 2.6 Program Specific Objectives (PSOs)

| PSO    | -1 | Enable students to get deep knowledge in the domain of VLSI Design and be able to solve complex problems in the field of Electronics and Communication Engineering. |

|--------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSO -2 |    | Enable students to carry out research work in emerging technologies and to pursue career in higher studies and research.                                            |

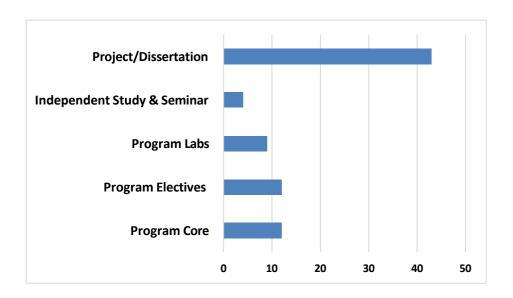

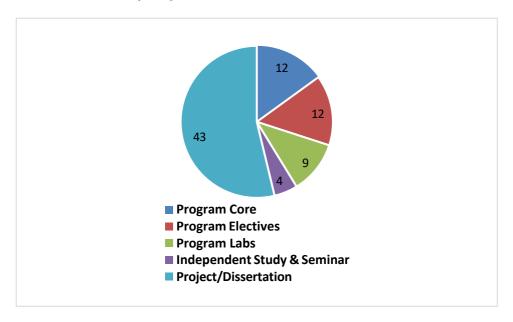

#### 3.1 Credit Distribution

#### 3.2 Semester wise Credit Structure

|        | Credits                     |                 |                                           |          |          |       |  |  |  |  |

|--------|-----------------------------|-----------------|-------------------------------------------|----------|----------|-------|--|--|--|--|

| S. No. | Category of Courses         | 1 <sup>st</sup> | 1 <sup>st</sup> Year 2 <sup>nd</sup> Year |          |          | Total |  |  |  |  |

|        |                             | Semester I      | Semester                                  | Semester | Semester |       |  |  |  |  |

|        |                             |                 | II                                        | III      | IV       |       |  |  |  |  |

| 1.     | Program Core                | 9               | 3                                         | -        | -        | 12    |  |  |  |  |

| 2.     | Program Electives           | 6               | 6                                         | -        | -        | 12    |  |  |  |  |

| 3.     | Program Labs                | Program Labs 3  |                                           | -        | -        | 9     |  |  |  |  |

| 4.     | Independent Study & Seminar | 2               | 2                                         | -        | -        | 4     |  |  |  |  |

| 5.     | Project/Dissertation        | -               | 3                                         | 20       | 20       | 43    |  |  |  |  |

|        | Total                       | 20              | 20                                        | 20       | 20       | 80    |  |  |  |  |

**Minimum Credits Required for Award of Degree = 80**

## 3.3 Credit Distribution (in %)

| Course Coding Pattern |                               |                             |  |  |  |  |

|-----------------------|-------------------------------|-----------------------------|--|--|--|--|

| Semester              | M. Tech in ECE                | M. Tech in ECE (VLSI Design |  |  |  |  |

|                       | Departmental Core Courses (   | Theory)                     |  |  |  |  |

| Autumn Semester       | ECEM (5/6)0x                  | ECVM (5/6)0x                |  |  |  |  |

|                       | (onwards)                     | (onwards)                   |  |  |  |  |

| Spring Semester       | ECEM (5/6)5x                  | ECVM (5/6)5x                |  |  |  |  |

|                       | (onwards)                     | (onwards)                   |  |  |  |  |

|                       | Departmental Elective Courses | (Theory)                    |  |  |  |  |

| Autumn Semester       | ECEM (5/6)2x                  | ECVM (5/6)2x                |  |  |  |  |

|                       | (onwards)                     | (onwards)                   |  |  |  |  |

| Spring Semester       | ECEM (5/6)7x                  | ECVM (5/6)7x                |  |  |  |  |

|                       | (onwards)                     | (onwards)                   |  |  |  |  |

|                       |                               |                             |  |  |  |  |

Numeric for  $1^{st}$  year = 5; Numeric for  $2^{nd}$  year = 6;

# Teaching Scheme for M. Tech in Electronics and Communication Engineering (VLSI Design)

|             | Semester I                                          |                 |   |    |         |  |  |  |  |

|-------------|-----------------------------------------------------|-----------------|---|----|---------|--|--|--|--|

| Course Code | Course Title                                        | L               | Т | P  | Credits |  |  |  |  |

| ECVM 5xx    | Core - I                                            | 3               | 0 | 3  |         |  |  |  |  |

| ECVM 5xx    | Core - II                                           | Core - II 3 0 0 |   |    |         |  |  |  |  |

| ECVM 5xx    | Core -III                                           | 3 0 0           |   |    |         |  |  |  |  |

| ECVM 5xx    | Elective-I                                          | 3 0 0           |   |    |         |  |  |  |  |

| ECVM 5xx    | Elective-II                                         |                 |   |    |         |  |  |  |  |

| ECVM 5xx    | Lab - I                                             | 0               | 0 | 6  | 3       |  |  |  |  |

| ECVM 507    | Independent Study and Seminar                       | 0               | 0 | 4  | 2       |  |  |  |  |

|             | Total Credits                                       | 15              | 0 | 10 | 20      |  |  |  |  |

|             | Semester II                                         |                 |   |    |         |  |  |  |  |

| Course Code | Course Title                                        | L               | Т | P  | Credit  |  |  |  |  |

| ECVM 5xx    | Core IV                                             | 3               | 0 | 0  | 3       |  |  |  |  |

| ECVM 5xx    | Elective-III                                        | 3               | 0 | 0  | 3       |  |  |  |  |

| ECVM 5xx    | Elective-IV                                         | 3               | 0 | 0  | 3       |  |  |  |  |

| ECVM 5xx    | Lab - II                                            | 0               | 6 | 3  |         |  |  |  |  |

| ECVM 5xx    | Lab - III                                           | 0               | 0 | 6  | 3       |  |  |  |  |

| ECVM 557    | Independent Study and Seminar                       | 0               | 0 | 4  | 2       |  |  |  |  |

| ECVM 558    | Minor Project                                       | 0               | 0 | 6  | 3       |  |  |  |  |

|             | Total Credits                                       | 9               | 0 | 22 | 20      |  |  |  |  |

|             | Semester III                                        |                 |   |    |         |  |  |  |  |

| Course Code | Course Title                                        | L               | Т | P  | Credit  |  |  |  |  |

| ECVM 604    | Dissertation I                                      | 0               | 0 | 32 | 16      |  |  |  |  |

| ECVM 602    | MOOCs Course – I/ Independent Study<br>Course - I   | 3               | 0 | 0  | 3       |  |  |  |  |

| ECVM 603    | Seminar - I                                         | 0               | 0 | 2  | 1       |  |  |  |  |

|             | Total Credits                                       | 3               | 0 | 34 | 20      |  |  |  |  |

|             | Semester IV                                         |                 |   |    |         |  |  |  |  |

| Course Code | Course Title                                        | L               | Т | P  | Credit  |  |  |  |  |

| ECVM 654    | Dissertation II                                     | 0               | 0 | 32 | 16      |  |  |  |  |

| ECVM 652    | MOOCs Course – II/ Independent Study<br>Course - II | 3               | 3 |    |         |  |  |  |  |

| ECVM 653    | Seminar - II                                        | 0               | 0 | 2  | 1       |  |  |  |  |

|             | Total Credits                                       | 3               | 0 | 34 | 20      |  |  |  |  |

#### Special Note for Selection of Massive Open Online Courses (MOOCs)/ Independent Study Courses

- Students are encouraged to take the above-mentioned MOOCs courses in their 3<sup>rd</sup> and 4<sup>th</sup> semesters preferably. The MOOCs courses can only be decided by the students in consultation with the Convener, DPGC (ECE) and HoD (ECE) and should be in allied/relevant area of VLSI or related to the list of elective courses provided in the scheme.

- However, students willing to take those above MOOCs courses during their 1<sup>st</sup> and 2<sup>nd</sup> semester are also allowed but their evaluation and marks to be credited during their 3<sup>rd</sup> and 4<sup>th</sup> semesters respectively as indicated above.

- If a student completes a MOOC course and submits the evaluation result by the end of 3<sup>rd</sup> and 4<sup>th</sup> semester respectively, the they will be exempted from appearing for the Institute examination in the respective Independent Study Course I (in the 3<sup>rd</sup> semester) and Independent Study Course II (in the 4<sup>th</sup> semester).

- A student failing to complete the MOOC courses will have to choose an Independent Study course-I (in the 3<sup>rd</sup> semester) and Independent Study Course II (in the 4<sup>th</sup> semester), (from the list of elective courses and also which is not running in that semester/ previously not studied by the concern student), have to complete (as per the Institute's procedure) the self-study and examinations as per the Institute's rules and regulations.

# List of Core Subjects

| S.<br>No. | Course Code | Course Title                       | L | Т | P | Credits | Core<br>Applicability          |

|-----------|-------------|------------------------------------|---|---|---|---------|--------------------------------|

| 1.        | ECVM 501    | Semiconductor Devices              | 3 | 0 | 0 | 3       | Core I + Core<br>II + Core III |

| 2.        | ECVM 502    | Digital IC Design                  | 3 | 0 | 0 | 3       | II + Core III                  |

| 3.        | ECVM 503    | Analog IC Design                   | 3 | 0 | 0 | 3       |                                |

| 4.        | ECVM 551    | System-on-Programmable Chip Design | 3 | 0 | 0 | 3       | Core IV                        |

## **List of Laboratory Subjects**

| S. No. | Course Code | Course Title                           | L | Т | P | Credits | Lab<br>Applicability |

|--------|-------------|----------------------------------------|---|---|---|---------|----------------------|

| 1.     | ECVM 505    | Analog and Digital Design Laboratory   | 0 | 0 | 6 | 3       | Lab I                |

| 2.     | ECVM 554    | High level Design Laboratory           | 0 | 0 | 6 | 3       | Lab II +             |

| 3.     | ECVM 555    | System-on-Programmable Chip Design Lab | 0 | 0 | 6 | 3       | Lab III              |

### **List of Elective Subjects**

| S. No. | Course<br>Code | Course Title                                                            | L                       | T | P | Credits | Elective<br>Applicability     |

|--------|----------------|-------------------------------------------------------------------------|-------------------------|---|---|---------|-------------------------------|

| 1.     | ECVM 520       | Real Time Signal Processing Systems                                     | 3                       | 0 | 0 | 3       | Elective I +<br>Elective II   |

| 2.     | ECVM 521       | VLSI Systems Design                                                     | 3                       | 0 | 0 | 3       |                               |

| 3.     | ECVM 522       | Embedded Systems & RTOS                                                 | 3                       | 0 | 0 | 3       |                               |

| 4.     | ECVM 523       | Architectural Design of IC's                                            | 3                       | 0 | 0 | 3       |                               |

| 5.     | ECVM 524       | VLSI Testing                                                            | 3                       | 0 | 0 | 3       |                               |

| 6.     | ECVM 525       | RF IC Design                                                            | 3                       | 0 | 0 | 3       |                               |

| 7.     | ECVM 526       | VLSI Technology                                                         | VLSI Technology 3 0 0 3 |   |   |         |                               |

| 8.     | ECVM 527       | VLSI Signal Processing                                                  | 3                       | 0 | 0 | 3       |                               |

| 9.     | ECVM 528       | Block chain Design and Use Cases                                        | 3                       | 0 | 0 | 3       |                               |

| 10.    | ECVM 570       | Low Power Design Techniques                                             | 3                       | 0 | 0 | 3       | Elective III +<br>Elective IV |

| 11.    | ECVM 571       | ECVM 571 Mapping Signal Processing Algorithm on 3 0 0 DSP Architectures |                         |   |   |         |                               |

| 12.    | ECVM 572       | MOS Devices Modelling and<br>Characterization                           | 3                       | 0 | 0 | 3       |                               |

| 13.    | ECVM 573       | Mixed Signal IC Design                                                  | 3                       | 0 | 0 | 3       |                               |

| 14.    | ECVM 574       | High Speed System Design (Board level)                                  | 3                       | 0 | 0 | 3       |                               |

| 15.    | ECVM 575       | Advanced Digital System Design                                          | 3                       | 0 | 0 | 3       |                               |

# **Curriculum in Detail (Core Courses)**

| Course Code                         |                                     | ECVM 50                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Semester: Odd<br>(Specify Odd/Even) |                                         | Semest                          | ter: I Session: Autumn                                                                                                                      |

|-------------------------------------|-------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Course Name                         |                                     | Semicondu                | ictor Dev                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ices                                |                                         |                                 |                                                                                                                                             |

| Credits                             |                                     | 3                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     | Contact                                 | Hours                           | 3                                                                                                                                           |

| Faculty                             |                                     | Coordinate               | or(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                     |                                         |                                 |                                                                                                                                             |

| (Names)                             |                                     | Teacher(s)<br>(Alphabeti |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     |                                         |                                 |                                                                                                                                             |

| Course<br>Objectives                |                                     |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     |                                         |                                 | f electronic devices and to train rtant applications.                                                                                       |

| Module No.                          |                                     | itle of the<br>Iodule    | List of T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>opics</b>                        |                                         |                                 |                                                                                                                                             |

| Unit I                              | Unit I Basic Semiconduc tor Physics |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vell- Boltzma<br>sms, - drift,      | ann and l<br>diffusion,<br>er lifetime  | Fermi-Di<br>thermio             | ty of states, distribution statistics irac, doping, carrier transport onic emission, and tunnelling; abination mechanisms – SHR,            |

| Unit II                             | Jı                                  | unctions                 | DC mod transient model; r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | lel, charge co<br>conditions, c     | ontrol mod<br>apacitance<br>aductor jui | del, I-V<br>model,<br>nctions – | ion – forward and reverse bias, characteristic, steady-state and reverse-bias breakdown, SPICE – fabrication, Schottky barriers, teristics. |

| Unit III MOS Capacitors and MOSFETs |                                     |                          | The MOS capacitor – fabrication, surface charge –accumulation, depletion, inversion, threshold voltage, C-V characteristics – low and high frequency; the MOSFET – fabrication, operation, gradual channel approximation, simple charge control model (SCCM), Pao-Sah and Schichman – Hodges models, I-V characteristic, second-order effects – Velocity saturation, short-channel effects, charge sharing model, hot-carrier effects, gate tunnelling; sub-threshold operation – drain induced barrier lowering (DIBL) effect, unified charge control model (UCCM), SPICE level 1, 2, and 3, and Berkeley short-channel IGFET model (BSIM). |                                     |                                         |                                 |                                                                                                                                             |

|                                     |                                     |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     |                                         |                                 |                                                                                                                                             |

| Uni | t IV                                                                                                    | MOSFETs<br>and HEMTs | MESFETs –fabrication, basic operation, Shockley and velocity saturation models, I-V characteristics, high-frequency response, backgating effect, SPICE model; HEMTs – fabrication, modulation (delta) doping, analysis of III-V heterojunctions, charge control, I-V characteristics, SPICE model.                                                                                                                 |  |  |  |  |

|-----|---------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Uni | t V                                                                                                     | BJTs and<br>HBTs     | BJTs – fabrication, basic operation, minority carrier distributions and terminal currents, I-V characteristic, switching, second-order effects – base narrowing, avalanche multiplication, high injection, emitter crowding, Kirk effect, etc.; breakdown, high-frequency response, Gummel Poon model, SPICE model; HBTs: - fabrication, basic operation, technological aspects, I-V characteristics, SPICE model. |  |  |  |  |

| Cou | essment                                                                                                 | Continuous E         | valuation 25% Mid Semester 25% End Semester 50%                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|     |                                                                                                         | 0                    | terial: Author(s), Title, Edition, Publisher, Year of Publication etc. (Text mals, Reports, Websites etc. in the IEEE format)                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 1.  | Ben G. Streetman, Solid State Electronic Devices, Prentice Hall, 1997.                                  |                      |                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 2.  | Richard S. Muller and Theodore I. Kamins, Device Electronics for Integrated Circuits, John Wiley, 1986. |                      |                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 3.  | S.M. Sze and Kwok K. Ng, Physics of Semiconductor Devices, 3rd edition, John-Wiley, 2006.               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 4.  | Donald N                                                                                                | Veamen, An Int       | roduction to Semiconductor Devices, McGraw-Hill Education, 2005.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Course Code          |                              |                                       |                                                                                                                                                                                                                                           |                                |                                                            | Semester: I Session:<br>Autumn<br>Odd |                                |

|----------------------|------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------|---------------------------------------|--------------------------------|

| Course Name          | DIC                          | GITAL IC DE                           | ESIGN                                                                                                                                                                                                                                     |                                |                                                            |                                       |                                |

| Credits              | 3                            |                                       |                                                                                                                                                                                                                                           |                                | Contact Hours                                              | 3                                     |                                |

| Faculty (Name:       | s)                           | Coordinat                             | or(s)                                                                                                                                                                                                                                     |                                |                                                            |                                       |                                |

|                      |                              | Teacher(s<br>(Alphabet                |                                                                                                                                                                                                                                           |                                |                                                            |                                       |                                |

| Course Objecti       | ves                          |                                       |                                                                                                                                                                                                                                           |                                | vel design of all dig<br>e, speed and powe                 | -                                     | g blocks and learn all<br>ion. |

| Course Outcom        | ies                          |                                       |                                                                                                                                                                                                                                           |                                |                                                            |                                       | Cognitive Levels               |

| CO1                  |                              |                                       |                                                                                                                                                                                                                                           |                                | natical methods<br>s of CMOS digital c                     |                                       | Understanding<br>(Level II)    |

| CO2                  |                              | CMOS comfunctions a                   | e to create models of moderately sized static<br>nbinational circuits that realize specified digital<br>and to optimize combinational circuit delay using<br>nodels and logical effort                                                    |                                |                                                            |                                       | Analyzing                      |

| CO3                  |                              | To be able<br>and comp<br>including f | are the                                                                                                                                                                                                                                   | tradeoff                       |                                                            |                                       |                                |

| CO4                  |                              | To be able<br>SRAM cell.              |                                                                                                                                                                                                                                           | <b>Analyzing</b><br>(Level IV) |                                                            |                                       |                                |

|                      | Title<br>Modu                |                                       | List of To                                                                                                                                                                                                                                | opics                          |                                                            |                                       |                                |

|                      |                              | iples and<br>S                        | Transisto<br>Characte                                                                                                                                                                                                                     | or Seconda                     | ic Conditions, MOS<br>tic and Dynamic<br>parameters, Stick |                                       |                                |

|                      |                              | oinational<br>Circuits                | complex                                                                                                                                                                                                                                   | _                              | its, Logical effort of<br>complex gates,                   |                                       |                                |

| III                  | Sequential Logic<br>Circuits |                                       |                                                                                                                                                                                                                                           |                                | d Registers, Timing                                        |                                       |                                |

|                      | _                            | timed cir<br>synchron                 | 'iming classification of digital systems, Synchronous Design, Self<br>imed circuit design, Synchronizers and arbiters, Clock synthesis<br>ynchronization using PLL, Distributed clocking using DLLs, Men<br>ore and Peripheral Circuitry. |                                |                                                            |                                       |                                |

| Course<br>Assessment | Conti                        | nuous Evalı                           | ation 259                                                                                                                                                                                                                                 | % Mid Sen                      | nester 25% End Se                                          | emester 50%                           | 6                              |

|    | ommended Reading material: Author(s), Title, Edition, Publisher, Year of Publication etc. (Text ks, Reference Books, Journals, Reports, Websites etc. in the IEEE format) |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Jan Rabaey, AnanthaChandrakasan, B Nikolic, "Digital Integrated Circuits: A Design Perspective", Prentice Hall of India, 2nd Edition, Feb 2003                            |

| 2. | N.Weste, K. Eshraghian, " Principles of CMOS VLSI Design", Addision Wesley, 2nd Edition, 1993                                                                             |

| 3. | K.Martin - Digital integrated circuit design                                                                                                                              |

| 4. | J.Kuo and J.Lou - Low voltage CMOS VLSI circuits                                                                                                                          |

| 5. | M J Smith, "Application Specific Integrated Circuits", Addisson Wesley, 1997                                                                                              |

| 6. | Sung-Mo Kang & Yusuf Leblebici, "CMOS Digital Integrated Circuits Analysis and Design", McGraw-Hill, 1998.                                                                |

| Course Code                                                                                                         |                          | ECVM 503                  |                                                                                                                                                                                                                                                                                                                                                                                                                                       | Semester: Odd<br>(specify Odd/Even)                                                              | Semester: I Session: Autumn                                                                                                                                                                                                                                                                                                            |      |  |  |

|---------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| <b>Course Name</b>                                                                                                  | !                        | ANALOG 1                  | NALOG IC DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

| Credits                                                                                                             | redits 3 Contact Hours 3 |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

| Faculty (Nam                                                                                                        | es)                      | Coordin                   | nator(s)                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                  |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

|                                                                                                                     |                          | Teache<br>(Alphal         | r(s)<br>petically)                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                  |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

| Course<br>Objectives                                                                                                |                          | and to e                  |                                                                                                                                                                                                                                                                                                                                                                                                                                       | ents with skills to desig                                                                        | uit design relevant to CMOS IC design<br>gn and analyze CMOS-based circuits and                                                                                                                                                                                                                                                        | ŗ    |  |  |

| Course<br>Outcomes:                                                                                                 |                          | •                         | Understan<br>To analyze<br>To design                                                                                                                                                                                                                                                                                                                                                                                                  | nding the MOS Operatio<br>e single-stage amplifier:                                              | onal amplifiers and VCO Circuits.                                                                                                                                                                                                                                                                                                      |      |  |  |

| Module No.                                                                                                          |                          | tle of the<br>odule       | List of T                                                                                                                                                                                                                                                                                                                                                                                                                             | opics                                                                                            |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

| Unit I                                                                                                              | -                        | OS<br>eration<br>d Models | Consider<br>Saturatio<br>Channel                                                                                                                                                                                                                                                                                                                                                                                                      | rations, MOS I/V Char<br>on, Transconductance,<br>length modulation, Sub<br>SPICE, Short Channel | evice Physics: Device Structure and Operation, General s, MOS I/V Characteristics, Finite Output Resistance in Fransconductance, Second Order effects: body effect, h modulation, Subthreshold conduction, MOS small signal E, Short Channel Effects: DIBL, velocity saturation, hot impact ionization, surface scattering.  (9 hours) |      |  |  |

| Unit II                                                                                                             | M(<br>Am                 | OS<br>nplifiers           | Amplifiers: Basic concepts, Single Stage Amplifiers: Basic Concepts, Common Source Stage: resistive load, diode connected load, current source load, triode load, source degeneration. Source Follower, Common Gate Stage, Cascode Stage. Folded cascode.  Differential Amplifiers: Single Ended and Differential Operation, Basic Differential Pair, Common Mode Response, Differential Pair with MOS loads, Gilbert Cell. (9 hours) |                                                                                                  |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

| Unit III Frequency Response of Amplifiers                                                                           |                          |                           | Passive and Active Current Mirrors: Basic Current Mirrors, Cascode Current Mirrors, Active Current Mirrors. Frequency Response of Amplifiers: Amplifier transfer function, General Considerations, Miller Effect, Common Source Stage, Source Followers, Common Gate Stage.  (9 hours)                                                                                                                                                |                                                                                                  |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

| Unit IV                                                                                                             |                          |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

| Course Assessment Continuous Evaluation 25% Mid Semester 25% End Semester 50%                                       |                          |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

|                                                                                                                     |                          | _                         |                                                                                                                                                                                                                                                                                                                                                                                                                                       | uthor(s), Title, Edition,<br>orts, Websites etc. in th                                           | Publisher, Year of Publication etc. (Texne IEEE format)                                                                                                                                                                                                                                                                                | ít – |  |  |

|                                                                                                                     |                          |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  | 2nd Edition, McGraw Hill Edition 2016.                                                                                                                                                                                                                                                                                                 |      |  |  |

| 2. Paul. R.Gray and Robert G. Meyer, "Analysis and Design of Analog Integrated Circuits", Wiley, 5th Edition, 2009. |                          |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  |                                                                                                                                                                                                                                                                                                                                        |      |  |  |

| 3. R. Jacob                                                                                                         | Bak                      | er, "CMOS                 | Circuit De                                                                                                                                                                                                                                                                                                                                                                                                                            | sign, Layout, and Simul                                                                          | lation", 3rd Edition, Wiley, 2010.                                                                                                                                                                                                                                                                                                     |      |  |  |

| 4. T. C. Caru<br>2012                                                                                               | usor                     | ne, D. A. Jol             | nns and K.                                                                                                                                                                                                                                                                                                                                                                                                                            | Martin, "Analog Integra                                                                          | rated Circuit Design", 2nd Edition, Wiley                                                                                                                                                                                                                                                                                              | 7,   |  |  |

| Course Code: ECVM<br>570                                                  | Open course<br>(YES/NO) | HM<br>Course<br>(Y/N)                                                                                                                                                                       | DC (Y/N)                                         |           | DE (Y/N)                    |  |  |  |  |  |

|---------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------|-----------------------------|--|--|--|--|--|

|                                                                           | No                      | No                                                                                                                                                                                          | No                                               |           | Yes                         |  |  |  |  |  |

| Type of Course                                                            | Theory                  |                                                                                                                                                                                             |                                                  |           |                             |  |  |  |  |  |

| Course Title                                                              | Low Power De            | esign Techn                                                                                                                                                                                 | iques                                            |           |                             |  |  |  |  |  |

| Course                                                                    |                         |                                                                                                                                                                                             |                                                  |           |                             |  |  |  |  |  |

| Coordinator                                                               | ml I D                  | MCID :                                                                                                                                                                                      | C                                                | 1 . 1     |                             |  |  |  |  |  |

| ·                                                                         | dissipation sou         | The Low Power VLSI Design course focuses on understanding power dissipation sources in digital circuits and applying low-power techniques at the device, circuit, logic, and system levels. |                                                  |           |                             |  |  |  |  |  |

| COURSE<br>OUTCOMES                                                        | circuit                 | ts.                                                                                                                                                                                         | nportance of low power<br>various sources of pov |           | Knowledge<br>(Level I)      |  |  |  |  |  |

|                                                                           | dissip                  | ation in CM(                                                                                                                                                                                |                                                  |           | Understanding<br>(Level II) |  |  |  |  |  |

|                                                                           | gate le                 | evel.                                                                                                                                                                                       | se the concept of pow                            |           | Analysis (Level<br>IV)      |  |  |  |  |  |

|                                                                           | reduc                   |                                                                                                                                                                                             | ues in Clock networks                            |           | Applying (Level<br>III)     |  |  |  |  |  |

| Semester                                                                  | Autumn:                 |                                                                                                                                                                                             | D .: 1                                           | 0 11      | m . 1                       |  |  |  |  |  |

|                                                                           | Lecture                 | Tutorial                                                                                                                                                                                    | Practical                                        | Credits   | Total<br>Teaching Hours     |  |  |  |  |  |

| Contact Hours                                                             |                         | 0                                                                                                                                                                                           | 0                                                | 3         | 36                          |  |  |  |  |  |

| Prerequisite<br>course code as per<br>proposed<br>course numbers          | NIL                     |                                                                                                                                                                                             |                                                  |           |                             |  |  |  |  |  |

| Prerequisite<br>Credits                                                   | NIL                     |                                                                                                                                                                                             |                                                  |           |                             |  |  |  |  |  |

| Equivalent course<br>codes as per<br>proposed course<br>and old<br>course | NIL                     |                                                                                                                                                                                             |                                                  |           |                             |  |  |  |  |  |

| codes as per<br>proposed course<br>numbers                                | NIL                     |                                                                                                                                                                                             |                                                  |           |                             |  |  |  |  |  |

| Text Books:                                                               | L., ,                   | <b>—</b>                                                                                                                                                                                    |                                                  |           |                             |  |  |  |  |  |

| 1.                                                                        | Title                   |                                                                                                                                                                                             | Low Power Digital VL                             | SI Design |                             |  |  |  |  |  |

|                                                                           | Author                  | Gary K. Y                                                                                                                                                                                   | eap                                              |           |                             |  |  |  |  |  |

|                                                                           | Publisher               | KAP                                                                                                                                                                                         |                                                  |           |                             |  |  |  |  |  |

|                                                                           | Edition                 | 2002                                                                                                                                                                                        |                                                  |           |                             |  |  |  |  |  |

| 2.                                                                        | Title                   | Low Pow                                                                                                                                                                                     | er Design Methodolog                             | gies      |                             |  |  |  |  |  |